- 您现在的位置:买卖IC网 > Sheet目录317 > CAT24C08TDI-GT3 (ON Semiconductor)8KB I2C SER EEPROM TSOT 23

�� �

�

CAT24C01,� CAT24C02,� CAT24C04,� CAT24C08,� CAT24C16�

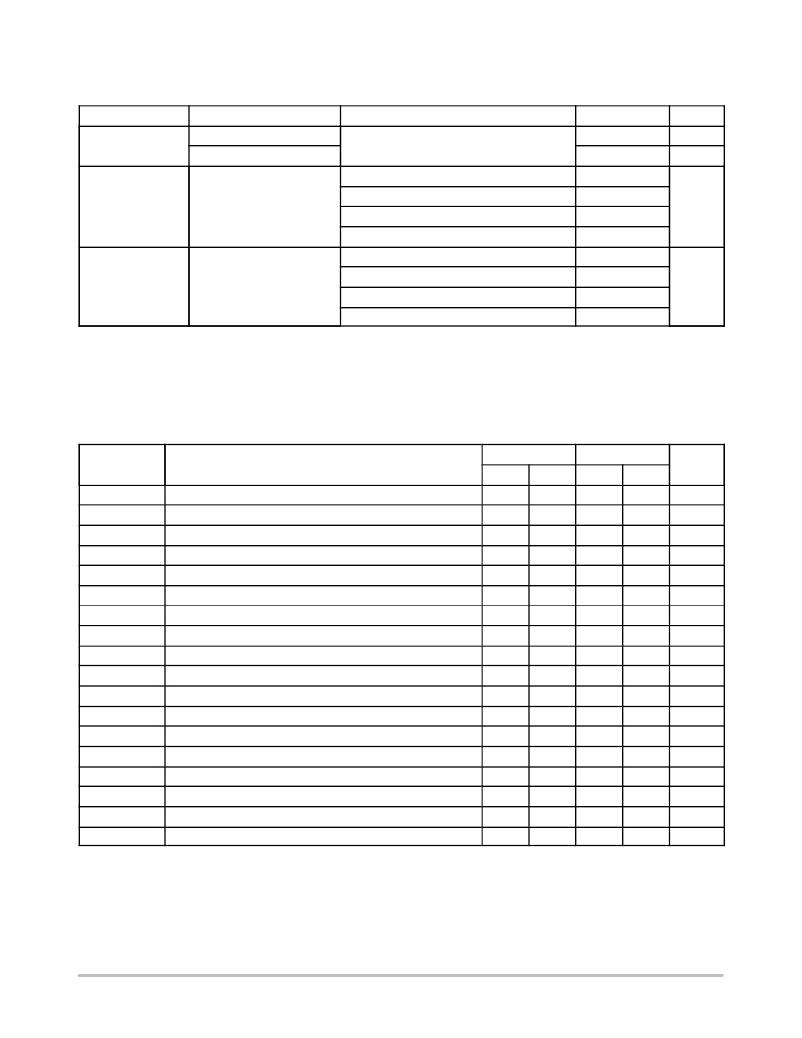

�Table� 5.� PIN� IMPEDANCE� CHARACTERISTICS�

�(V� CC� = 1.8 V to 5.5 V, T� A� =� ?� 40� °� C� to� +125� °� C� and� V� CC� =� 1.7� V� to� 5.5� V,� T� A� =� ?� 40� °� C� to� +85� °� C,� unless� otherwise� specified.)�

�Symbol�

�C� IN� (Note� 4)�

�I� WP� (Note� 5)�

�Parameter�

�SDA� Pin� Capacitance�

�Other� Pins�

�WP� Input� Current�

�Conditions�

�V� IN� =� 0� V,� f� =� 1.0� MHz,� V� CC� =� 5.0� V�

�V� IN� <� V� IH� ,� V� CC� =� 5.5� V�

�Max�

�8�

�6�

�130�

�Units�

�pF�

�pF�

�m� A�

�V� IN� <� V� IH� ,� V� CC� =� 3.3� V�

�V� IN� <� V� IH� ,� V� CC� =� 1.7� V�

�V� IN� >� V� IH�

�120�

�80�

�2�

�I� A� (Note� 5)�

�Address� Input� Current�

�(A0,� A1,� A2)�

�Product� Rev� H:� CAT24C02�

�Product� Rev� K:� CAT24C04,�

�CAT24C08,� CAT24C16�

�V� IN� <� V� IH� ,� V� CC� =� 5.5� V�

�V� IN� <� V� IH� ,� V� CC� =� 3.3� V�

�V� IN� <� V� IH� ,� V� CC� =� 1.7� V�

�50�

�35�

�25�

�m� A�

�V� IN� >� V� IH�

�2�

�4.� These� parameters� are� tested� initially� and� after� a� design� or� process� change� that� affects� the� parameter� according� to� appropriate� AEC� ?� Q100�

�and� JEDEC� test� methods.�

�5.� When� not� driven,� the� WP,� A0,� A1� and� A2� pins� are� pulled� down� to� GND� internally.� For� improved� noise� immunity,� the� internal� pull� ?� down� is�

�relatively� strong;� therefore� the� external� driver� must� be� able� to� supply� the� pull� ?� down� current� when� attempting� to� drive� the� input� HIGH.� To�

�conserve� power,� as� the� input� level� exceeds� the� trip� point� of� the� CMOS� input� buffer� (~� 0.5� x� VCC),� the� strong� pull� ?� down� reverts� to� a� weak�

�current� source.�

�Table� 6.� A.C.� CHARACTERISTICS�

�(Note� 6)� (V� CC� =� 1� .8 V to 5.5 V, T� A� =� ?� 40� °� C to +125� °� C and V� CC� = 1.7 V to 5.5 V, T� A� =� ?� 40� °� C� to� +85� °� C,� unless� otherwise� specified.)�

�Standard�

�Fast�

�Symbol�

�Parameter�

�Min�

�Max�

�Min�

�Max�

�Units�

�F� SCL�

�t� HD:STA�

�t� LOW�

�t� HIGH�

�t� SU:STA�

�t� HD:DAT�

�t� SU:DAT�

�t� R�

�t� F� (Note� 6)�

�t� SU:STO�

�t� BUF�

�t� AA�

�t� DH�

�T� i� (Note� 6)�

�t� SU:WP�

�t� HD:WP�

�t� WR�

�t� PU� (Notes� 7,� 8)�

�Clock� Frequency�

�START� Condition� Hold� Time�

�Low� Period� of� SCL� Clock�

�High� Period� of� SCL� Clock�

�START� Condition� Setup� Time�

�Data� In� Hold� Time�

�Data� In� Setup� Time�

�SDA� and� SCL� Rise� Time�

�SDA� and� SCL� Fall� Time�

�STOP� Condition� Setup� Time�

�Bus� Free� Time� Between� STOP� and� START�

�SCL� Low� to� Data� Out� Valid�

�Data� Out� Hold� Time�

�Noise� Pulse� Filtered� at� SCL� and� SDA� Inputs�

�WP� Setup� Time�

�WP� Hold� Time�

�Write� Cycle� Time�

�Power� ?� up� to� Ready� Mode�

�4�

�4.7�

�4�

�4.7�

�0�

�250�

�4�

�4.7�

�100�

�0�

�2.5�

�100�

�1000�

�300�

�3.5�

�100�

�5�

�1�

�0.6�

�1.3�

�0.6�

�0.6�

�0�

�100�

�0.6�

�1.3�

�100�

�0�

�2.5�

�400�

�300�

�300�

�0.9�

�100�

�5�

�1�

�kHz�

�m� s�

�m� s�

�m� s�

�m� s�

�m� s�

�ns�

�ns�

�ns�

�m� s�

�m� s�

�m� s�

�ns�

�ns�

�m� s�

�m� s�

�ms�

�ms�

�6.� Test� conditions� according� to� “AC� Test� Conditions”� table.�

�7.� Tested� initially� and� after� a� design� or� process� change� that� affects� this� parameter.�

�8.� t� PU� is� the� delay� between� the� time� V� CC� is� stable� and� the� device� is� ready� to� accept� commands.�

�http://onsemi.com�

�3�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CAT24C128HU4IGT3

IC EEPROM 128KB I2C SRL 8UDFN

CAT24C164YI-G

IC EEPROM SERIAL 16KB I2C 8TSSOP

CAT24C208WI-GT3

IC EEPROM SER 8KB 400KHZ 8SOIC

CAT24C21LI

IC EEPROM SERIAL 1KB DUAL 8PDIP

CAT24C256XI-T2

IC EEPROM 256KBIT 400KHZ 8SOIC

CAT24C32HU3I-GT3

IC EEPROM 32KB I2C SERIAL 8UDFN

CAT24C32TSI-T3

IC EEPROM SRL 32KB I2C 5TSOP

CAT24C512HU5IGT3

IC EEPROM SRL 512KB I2C 8UDFN

相关代理商/技术参数

CAT24C08VP21-GT3

制造商:Rochester Electronics LLC 功能描述: 制造商:Catalyst Semiconductor 功能描述:

CAT24C08VP2GI-T3

制造商:Rochester Electronics LLC 功能描述: 制造商:Catalyst Semiconductor 功能描述:

CAT24C08VP2I-GT3

功能描述:电可擦除可编程只读存储器 8K-Bit I2C Serial RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

CAT24C08WE-G

制造商:ON Semiconductor 功能描述:

CAT24C08WE-GT3

制造商:ON Semiconductor 功能描述:

CAT24C08WGE

制造商:Rochester Electronics LLC 功能描述: 制造商:Catalyst Semiconductor 功能描述:

CAT24C08WGI

制造商:Rochester Electronics LLC 功能描述: 制造商:Catalyst Semiconductor 功能描述:

CAT24C08WI-G

功能描述:电可擦除可编程只读存储器 (1024x8) 8K 1.8-5.5 RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8